Automatikus optikai BGA átdolgozó állomás

Széles körben használják mobilok, laptopok, számítógépek, TV-k, klímaberendezések alaplapjainak chipszintű javításában. Magas sikeres javítási rátával és magas fokú automatizálással rendelkezik, és sok emberi erőfeszítést takarít meg. Mi ennek a gépnek a professzionális gyártója vagyunk, és ez a gép raktáron van.

Leírás

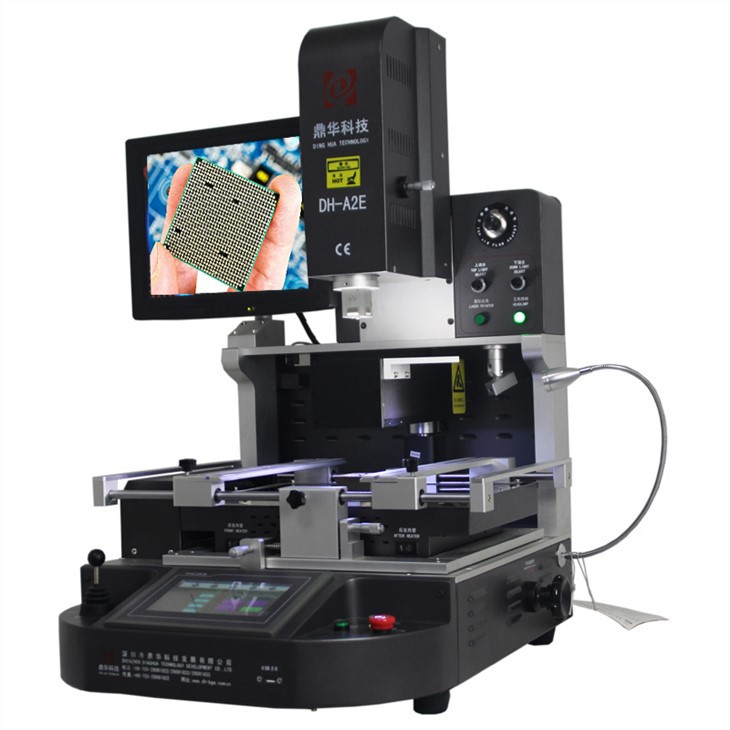

Automatikus optikai BGA átdolgozó állomás

1. Az Auto Optical BGA Rework Station alkalmazása

Számítógép alaplapja, okostelefon, laptop, MacBook logikai kártya, digitális kamera, légkondicionáló, TV és egyéb elektronikai eszközök

berendezések az orvosi iparból, kommunikációs iparból, autóiparból stb.

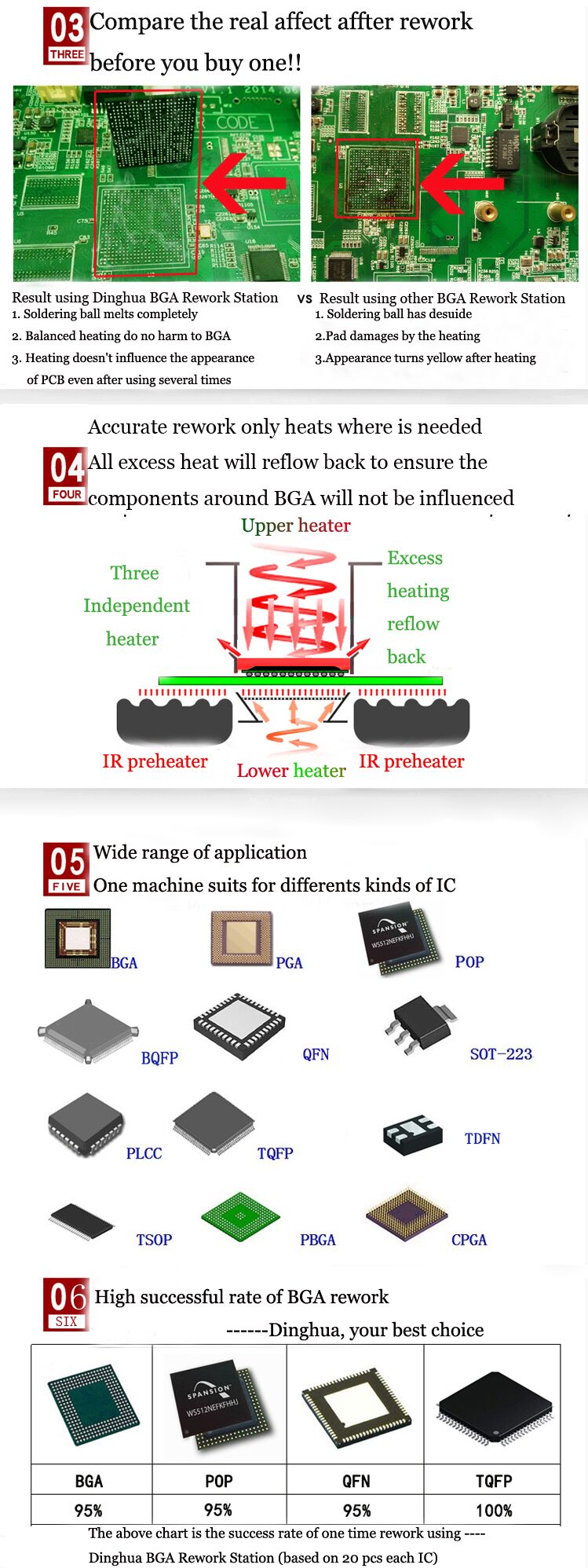

Különböző típusú chipekhez alkalmas: BGA,PGA,POP,BQFP,QFN,SOT223,PLCC,TQFP,TDFN,TSOP,PBGA,CPGA,LED chip.

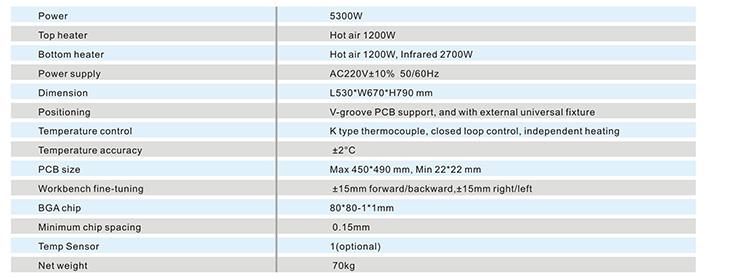

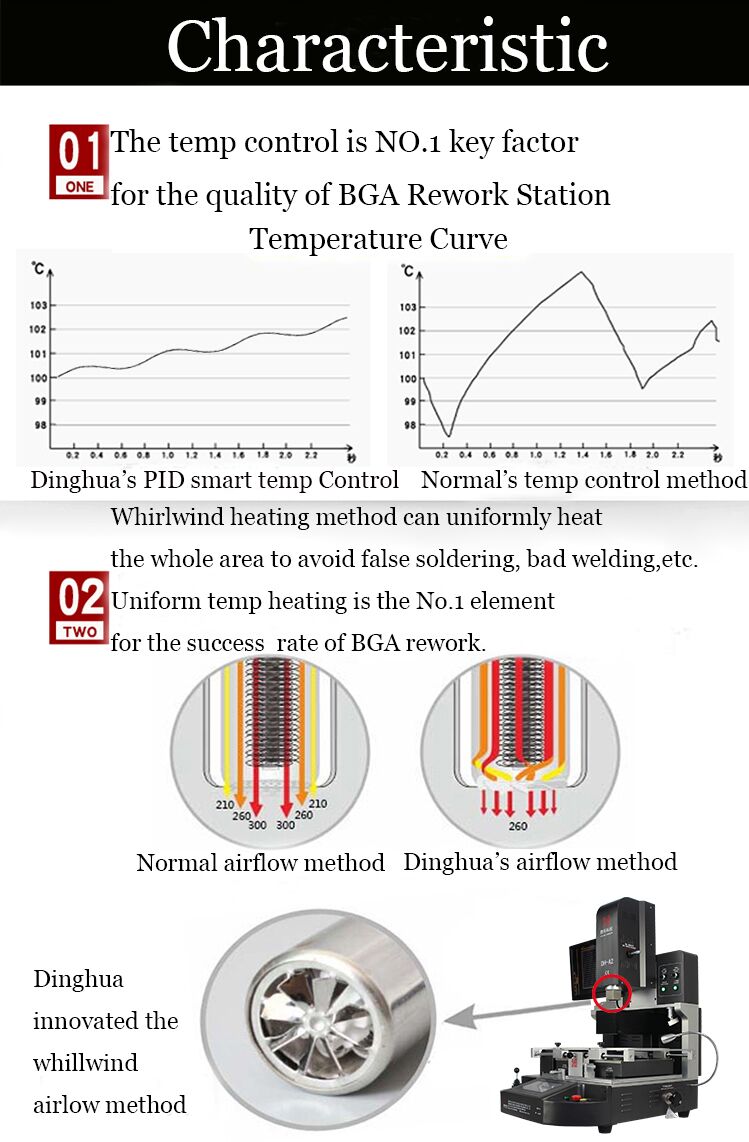

2. Az Auto Optical BGA Rework Station termékjellemzői

•A chip szintű javítások sikeressége magas. A kiforrasztás, szerelés és forrasztás automatikus.

• Az optikai igazítású CCD-kamerával minden forrasztási kötés pontos beállítása garantálható.

•A 3 független fűtési területtel precíz hőmérsékletszabályozás biztosítható. A gép beállíthatja és mentheti

1 millió hőmérsékleti profil.

• A beépített vákuum a szerelőfejben automatikusan felveszi a BGA chipet a kiforrasztás befejezése után.

3. Az Auto Optical BGA Rework Station specifikációja

4. Az Auto Optical BGA Rework Station részletei

CCD kamera (precíz optikai igazítási rendszer); 2.HD digitális kijelző ; 3. Mikrométer (a forgács szögének beállítása);

4.3 független fűtőtestek (meleg levegő és infravörös); 5. Lézeres pozicionálás ; 6. HD érintőképernyős interfész, PLC vezérlés;

7. Led fényszóró ; 8. Joystick vezérlés .

5. Miért válassza az Auto Optical BGA Rework Stationünket?

6. Az Auto Optical BGA Rework Station tanúsítványa

7. Az Auto Optical BGA Rework Station csomagolása és szállítása

8.GYIK

Hogyan teszteljük a chipet?

Kezdeti rendszerszintű chipteszt

Az SoC mély szubmikron folyamatokon alapul, így az új Soc eszközök tesztelése teljesen új megközelítést igényel. Mivel minden funkcionális komponens

saját tesztelési követelményei vannak, a tervezőmérnöknek a tervezési folyamat korai szakaszában teszttervet kell készítenie.

Meg kell valósítani az SoC eszközök blokkról blokkjára vonatkozó teszttervet: megfelelően konfigurált ATPG eszközök a logikai teszteléshez; rövid tesztidő; új nagysebességű

hibamodellek és több memória vagy kis tömb tesztek. A gyártósor esetében a diagnosztikai módszer nemcsak megtalálja a hibát, hanem elkülöníti a

hibás csomópont a működő csomópontból. Ezenkívül lehetőség szerint tesztelési multiplexelési technikákat kell alkalmazni a tesztidő megtakarítása érdekében. A magasan

Az integrált IC-tesztelés, az ATPG és az IDDQ tesztelhető tervezési technikái erőteljes hibaleválasztó mechanizmussal rendelkeznek.

Egyéb tényleges paraméterek, amelyeket előre meg kell tervezni, többek között a szkennelendő tűk száma és a memória mennyisége az egyes érintkezők végén.

A határellenőrzések beágyazhatók az SoC-be, de nem korlátozódnak a kártyákon vagy a többchipes modulokon végzett összekapcsolási tesztekre.

Bár a chip mérete csökken, egy chip még mindig több milliótól 100 millió tranzisztorig tud csomagolni, és a tesztmódok száma soha nem látott mértékben nőtt

szinteket, ami hosszabb tesztciklusokat eredményez. Ez a probléma tesztelhető. Mode tömörítés megoldani , a tömörítési arány elérheti a 20 százalékról 60 százalékra. A mai nagyszabású

chip tervezés, a kapacitásproblémák elkerülése érdekében olyan tesztszoftvereket kell találni, amelyek 64-bites operációs rendszereken futnak.

Ezenkívül a tesztszoftverek új tesztelési problémákkal szembesülnek, amelyeket a mikron alatti mély folyamatok és a növekvő gyakoriság okoz. A múltban az ATPG teszt mód

a statikus blokkoló hibák tesztelése már nem volt alkalmazható. A hagyományos eszközökhöz funkcionális minták hozzáadása megnehezítette az új hibák felkutatását. Jobb megközelítés az

osztályozza a múltbeli funkcionális mód csoportokat, hogy meghatározza, mely hibák nem észlelhetők, majd hozzon létre egy ATPG módot a hiányzó hibatípusok rögzítésére.

A tervezési kapacitás növekedésével és a tranzisztoronkénti vizsgálati idő csökkenésével a sebességgel kapcsolatos problémák megtalálása és az áramkör időzítésének ellenőrzése érdekében szinkron vizsgálati módszert kell alkalmazni.

alkalmazni kell. A szinkron tesztelésnek több hibamodellt is magában kell foglalnia, beleértve a tranziens modelleket, az útvonalkéséseket és az IDDQ-t.

Egyes iparági vállalatok úgy vélik, hogy a blokkoló, funkcionális és tranziens/útkésleltetési hibák kombinálása lehet a leghatékonyabb tesztstratégia. Mélyre

szubmikron chipek és nagyfrekvenciás működés, tranziens és útkésleltetés tesztelése még fontosabb.

A tesztmag szinkronizálása során felmerülő ATE pontosság problémájának megoldásához és a költségek csökkentéséhez új módszert kell találni, amely leegyszerűsíti a

a teszteszközt (tranziens és útkésleltetési teszt pontos órajelet igényel a vizsgálóeszköz interfészén), Biztosítja, hogy a jel kellően pontos legyen a teszt során.

Mivel az SoC memóriablokkban nagy a gyártási hibák lehetősége, a memória BIST-nek rendelkeznie kell diagnosztikai funkcióval. Amint megtalálják a problémát,

a hibás címegység leképezhető a tartalék címegység redundáns memóriájába, és az észlelt hibacím eldobásra kerül. Kerülje a kidobást

az egész drága chipet.

A kis beágyazott memóriablokkok tesztelésével nincs szükség további kapukra vagy vezérlőlogikára. Például a vektorkonverziós tesztelési technikák képesek konvertálni

a funkcionális módokat szkennelési módok sorozatává.

A BIST metódussal ellentétben a bypass memóriablokk funkcionális bemenete nem igényel további logikát. Mivel nincs szükség további tesztlogikára, a SoC

A fejlesztőmérnökök újra felhasználhatják a múltban kialakított tesztmintákat.

A fejlett ATPG eszközök nemcsak párhuzamosan tesztelik a makrókat, hanem azt is meghatározzák, hogy vannak-e ütközések, valamint részletezik, hogy mely makrók tesztelhetők párhuzamosan, és melyek

a makrókat nem lehet párhuzamosan tesztelni. Ezen túlmenően ezek a makrók akkor is hatékonyan tesztelhetők, ha a makró órája megegyezik a letapogatási órával (például szinkron memória).

Jelenleg nincs elég tesztpont a sűrű kétoldalas táblán, és minden összetett chipet fel kell szerelni határszkenner áramkörrel. Nélkül

a határellenőrzés, a táblaszintű gyártási hibák keresése meglehetősen nehézkes és nem is található. A határellenőrzéssel a táblaszintű tesztelés rendkívül egyszerű

és független a chipen belüli logikai áramkörtől. A határellenőrzés az ATPG módot a chip szkennelési láncához is konfigurálhatja a gyártás bármely szakaszában.